# WiMax: OFDM Synchronization on the picoArray

## **Summary**

The 802.16a-2003 standard specifies three different physical (PHY) layers, a host of possible configurations (e.g. TDD/FDD, channel bandwidth) and a number of optional features. The flexibility in the standard, limited availability of CPE equipment and time-to-market pressure make a software solution highly desirable, especially for the BS. However, the sampling rates involved make a full baseband implementation on single-processor DSPs untenable.

The picoArray<sup>™</sup> combines the programmability of a traditional high-end DSP with the performance of a FPGA/ASIC. The picoArray<sup>™</sup> is ideally suited for implementing the full baseband for the 802.16 suite of protocols. This application note looks in detail at an implementation of the receiver synchronization block for the WirelessMAN-OFDM uplink.

### **Table of Contents**

| 1 IN   | INTRODUCTION3                                      |    |  |  |  |

|--------|----------------------------------------------------|----|--|--|--|

| 2 W    | VIRELESSMAN-OFDM                                   | 3  |  |  |  |

| 2.1    | UPLINK DATA PREAMBLE                               |    |  |  |  |

| 2.2    | RECEIVER SYNCHRONIZATION                           | 5  |  |  |  |

| 3 TI   | HE PC102 PICOARRAY™                                | 6  |  |  |  |

| 3.1    | ARRAY ELEMENTS                                     | 6  |  |  |  |

| 3.2    | PICOBUS SWITCHING FABRIC                           | 7  |  |  |  |

| 4 U    | JPLINK PREAMBLE DETECTION ON THE PICOARRAY™        | 8  |  |  |  |

| 4.1    | Preamble Detection                                 |    |  |  |  |

| 4.2    | PICOARRAY <sup>TM</sup> IMPLEMENTATION             | 9  |  |  |  |

| 4.3    | A COMPLETE SYNCHRONIZATION BLOCK                   | 10 |  |  |  |

| 4.4    | TEST RESULTS                                       | 11 |  |  |  |

| 5 A    | APPENDIX: SOURCE CODE                              | 13 |  |  |  |

| 5.1    | SYNC                                               | 13 |  |  |  |

| 5.2    | BufferRx                                           | 15 |  |  |  |

| 5.3    | CALCCORRENGY                                       | 17 |  |  |  |

| 5.4    | CALCV                                              | 19 |  |  |  |

| 5.5    | SYNCCTRL                                           | 21 |  |  |  |

| 5.6    | TrackCorrEngy                                      | 23 |  |  |  |

|        |                                                    |    |  |  |  |

|        | of Figures E 1 - UPLINK PREAMBLE                   | 4  |  |  |  |

|        |                                                    |    |  |  |  |

|        | E 2 – 'SYNC' STRUCTURAL ENTITY                     |    |  |  |  |

| ⊢IGURE | E 3 - PICOARRAY PREAMBLE DETECTION VS MATLAB MODEL |    |  |  |  |

## **Abbreviations**

**AE** Array Element

ASIC Application Specific Integrated Circuit

**AWGN** Additive White Gaussian Noise

**BS** Basestation

**BWA** Broadband Wireless Access

**CP** Cyclic Prefix

**CPE** Customer Premises Equipment

**DL** Downlink

DSP Digital Signal ProcessorFDD Frequency Division DuplexFFT Fast Fourier Transform

**FPGA** Field Programmable Gate Array

LIW Long Instruction Word NLOS Non Line Of Sight

**OFDM** Orthogonal Frequency Division Multiplexing

PDU Protocol Data Unit

PHY Physical layer

PMP Point to Multipoint

SS Subscriber Station

TDD Time Division Duplex

**UL** Uplink

picoChip Designs Ltd. Page 2 of 24

#### 1 Introduction

The picoArray<sup>™</sup> is a multi-processor IC which integrates hundreds of processing elements into a single array. The individual elements have been optimized for signal processing and wireless algorithm computation and control. The result is a general purpose wireless communications processor, capable of executing all contemporary wireless standards, which combines the computational density of a dedicated ASIC with the programmability of a traditional high-end Digital Signal Processor (DSP).

WiMax is the industry forum name associated with the 802.16 suite of standards for broadband wireless access (BWA). WiMax offers raw bit rates in excess of 70Mbps (on a 20MHz channel), quality of service, authentication and data encryption over a metropolitan area.

Much of the focus is on the standard (currently 802.16a-2003) defined for NLOS operation in the licensed and unlicensed bands in the 2-11GHz range. Of particular interest are the physical (PHY) layers using orthogonal frequency division multiplexing (OFDM) given their simplicity and robustness in the presence of multipath.

The performance and flexibility offered by the picoArray  $^{TM}$  make it the ideal platform for implementing the plethora of options associated with a full WiMax BS baseband solution. This application note looks in detail at a picoArray  $^{TM}$  implementation of the receiver synchronization block for the WirelessMAN-OFDM PHY layer.

An overview of the receiver synchronization requirements and preamble used in the WirelessMAN-OFDM uplink is given in section 2. The key features of the PC102 picoArray<sup>TM</sup> are described briefly in section 3 to assist understanding. A picoArray<sup>TM</sup> implementation for obtaining coarse symbol timing is then given in section 4. This is complemented by a full source listing in section 5.

NOTE: The implementation presented in this application note is for illustrative purposes only. No claim is made with regard to conformance with the relevant standards.

### 2 WirelessMAN-OFDM

The WirelessMAN-OFDM PHY is one of the three physical layers defined in the 802.16a-2003 for NLOS operation in the 2-11GHz range. Each OFDM symbol consists of 256 sub-carriers. A cyclic prefix (CP) is added before each OFDM symbol for collecting the multipath associated with the previous symbol. For data symbols, 192 sub-carriers are data bearing, 8 are used as pilots and the remaining are used as guard bands at the lower and upper frequency extremes.

WiMax specifies a framed (burst) mode of operation but leaves the definition of the actual frame structure to the individual PHYs. In point-to-multipoint (PMP) mode, the OFDM PHY supports a frame consisting of a downlink (DL) sub-frame and an uplink (UL) sub-frame.

An uplink sub-frame consists of:

- contention intervals scheduled for initial ranging and bandwidth request purposes, and

- one or multiple UL PHY PDUs, each transmitted from a different subscriber station (SS).

An uplink PHY PDU consists of only one burst, which is made up of a short preamble and an integer

picoChip Designs Ltd. Page 3 of 24

number of OFDM symbols.

## 2.1 Uplink Data Preamble

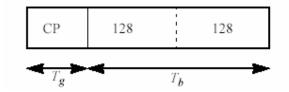

In the uplink, the data preamble consists of an OFDM symbol containing 2 times 128 samples (in the time-domain) preceded by a cyclic prefix whose length is the same as the cyclic prefix in the traffic mode. This is shown in Figure 1.

Figure 1 - Uplink Preamble

The preamble symbol is defined in the frequency domain as shown in Table 1. The repeating halves of the preamble symbol (in the time domain) are achieved by setting all odd numbered sub-carriers to null. This effectively makes the data preamble unique as:

- Periods of inactivity are marked by nulls (or AWGN) on all sub-carriers.

- Data symbols will have non-zero values on odd-numbered data sub-carriers.

| $P(-100:100) = sqrt(2)*sqrt(2)*{}$                                      | sub-carrier position |

|-------------------------------------------------------------------------|----------------------|

| 1, 0,-1, 0,-1, 0,-1, 0, 1, 0, 1, 0,                                     | [-100:-89]           |

| 1, 0, 1, 0,-1, 0, 1, 0,-1, 0,-1, 0,-1,                                  | [-88:-76]            |

| 0, 1, 0,-1, 0, 1, 0, 1, 0, 1, 0, 1,                                     | [-75:-64]            |

| 0,-1, 0, 1, 0, 1, 0, 1, 0,-1, 0, 1, 0,                                  | [-63:-51             |

| -1, 0, 1, 0, 1, 0, -1, 0, -1, 0, 1, 0,                                  | [-50:-39]            |

| -1, 0, 1, 0,-1, 0, 1, 0, 1, 0,-1, 0, 1,                                 | [-38:-26]            |

| 0, 1, 0,-1, 0,-1, 0,-1, 0, 1, 0,-1,                                     | [-25:-14]            |

| 0,-1, 0,-1, 0,-1, 0,-1, 0, 1, 0, 1, 0,                                  | [-13:-1]             |

| 0,                                                                      | [0]                  |

| 0, 1, 0,-1, 0,-1, 0, 1, 0,-1, 0, 1, 0,                                  | [1:13]               |

| 1, 0, 1, 0, 1, 0, -1, 0, 1, 0, 1, 0,                                    | [14:25]              |

| 1, 0, 1, 0,-1, 0, 1, 0,-1, 0,-1, 0,-1,                                  | [26:38]              |

| 0,-1, 0, 1, 0, 1, 0,-1, 0, 1, 0,-1,                                     | [39:50]              |

| 0,-1, 0,-1, 0,-1, 0,-1, 0,-1, 0,-1, 0,                                  | [51:63]              |

| -1, $0$ , $1$ , $0$ , $1$ , $0$ , $1$ , $0$ , $-1$ , $0$ , $-1$ , $0$ , | [64:75]              |

| -1, 0, 1, 0, 1, 0, -1, 0, -1, 0, -1, 0, 1,                              | [76:88]              |

| 0,-1, 0,-1, 0, 1, 0,-1, 0,-1, 0,-1}                                     | [89:100]             |

Table 1 - Sub-carrier values for UL preamble

The uniqueness of the uplink data preamble and its repetitive structure (in the time-domain) simplify the task of detecting the start of each uplink burst. Symbol timing can be achieved by correlating received samples separated by  $\frac{1}{2}$  an OFDM symbol. This is discussed in more detail in the next section.

picoChip Designs Ltd. Page 4 of 24

#### 2.2 Receiver Synchronization

Achieving receiver synchronization for OFDM involves detecting the start of each OFDM symbol and detecting and correcting any frequency offsets in the received signal. Detecting and correcting any frequency offset is especially important for OFDM as even a small offset can result in the orthogonality between sub-carriers being destroyed at the output of the FFT. Due to the presence of the CP, the requirements for symbol timing appear less stringent. The symbol can be deemed to start at any point within the CP not affected by multipath from the previous symbol. An early symbol start manifests as a phase rotation in the sub-carrier values at the output of the FFT. However, an early symbol start can degrade the equalization performance.

Coarse symbol timing can be obtained in the BS receiver by exploiting the repetitive structure of the uplink data preamble. For a (1x sampled) received signal r(k), two correlation values are calculated on a sample-by-sample basis:

$$\text{Equation 1} \qquad P(k) = \sum_{n=k-255}^{n=k-128} \!\!\! r(n) \times r^*(n+128) \quad E(k) = \sum_{n=k-255}^{n=k} \!\!\! r(n) \times r^*(n)$$

In the absence of noise and sampling errors:

The presence of the CP will actually cause v(k) to reach 1 for several samples before the actual end of the preamble symbol. The plateau in v(k) makes it difficult to determine the symbol timing precisely, hence the name coarse symbol timing. Selecting the coarse symbol timing so that it errs towards an early symbol start (i.e. within the CP) is acceptable for the reason given above. Fine symbol timing can be performed in the frequency domain to locate the symbol start more accurately. This, however, is beyond the scope of this application note. Noise and sampling errors (such as aperture jitter) will result in v(k) falling short of 1 at the end of the preamble.

A frequency offset may comprise of; (a) an integer number of sub-carrier spacings plus (b) a fraction of a sub-carrier spacing. The fractional frequency offset needs to be corrected before the received signal can be processed by the FFT. The fractional frequency offset can be determined from the value of P(k) selected by coarse symbol timing.

$$angle(P(k))$$

(radians)  $\propto$  fractional frequency offset (Hz)

picoChip Designs Ltd. Page 5 of 24

# 3 The PC102 picoArray<sup>™</sup>

An overview of the salient features of the PC102 picoArray<sup>TM</sup> is given here in order to understand the OFDM receiver synchronization block described in section 4. Reference is made to the source code given in section 5.2 for the receive buffer for illustrative purposes.

The PC102 consists of an array of processors or array elements interconnected by a high-speed switching fabric called the picoBus.

## 3.1 Array Elements

The PC102 contains four different types of array elements (AEs) which are detailed in Table 2. Minor differences exist between the three programmable AE types (STAN2, MEM2 and CTRL2). These differences include the size of instruction/data memory, additional processing unit and instructions supported (e.g. multiply-accumulate, multiply). A long instruction word (LIW) of upto 64bits allows upto 3 execution units to be targeted in a single cycle (160MHz). Each AE has a number of ports for communicating with other AEs within the array.

In addition to the STAN2, MEM2 and CTRL2 AE types specified in Table 2, software for the PC102 can also be targeted at the ANY2 AE type implying that:

- the function does not use any AE-specific instructions, and

- the code and data memory requirements can be met by all AE types.

|                          | Description                                                         | Number | Memory    |

|--------------------------|---------------------------------------------------------------------|--------|-----------|

| Туре                     |                                                                     |        | (Bytes)   |

| STAN2                    | Standard                                                            | 240    | 768       |

|                          | A standard AE type includes multiply-accumulate peripheral as well  |        |           |

|                          | as special instructions optimized for CDMA spread & de-spread.      |        |           |

|                          | Memory is divided between 512 bytes code and 256 bytes data.        |        |           |

| MEM2                     | Memory                                                              | 64     | 8,704     |

|                          | An AE having multiply unit and additional memory.                   |        |           |

|                          | Memory division between code and data is configurable.              |        |           |

| FAU                      | Function Accelerator Unit                                           | 14     | n/a       |

|                          | A co-processor optimised for specific signal processing tasks (FEC, |        |           |

|                          | preamble detect, FHT, etc). Includes dedicated hardware for trellis |        |           |

|                          | operations.                                                         |        |           |

| CTRL2                    | Control                                                             | 4      | 65,536    |

|                          | An AE type with a multiply unit and larger amounts of data and      |        |           |

|                          | instruction memory optimized for the implementation of basestation  |        |           |

|                          | control functionality.                                              |        |           |

|                          | Memory division between code and data is configurable.              |        |           |

| Totals per PC102 device: |                                                                     |        | 1,003,520 |

Table 2: PC102 processor variants and memory distribution

Software, written in C or ASM, is targeted at an AE type depending on the processing units used and memory required. Section 5.2 shows the ASM source between the *code* (line 55) and *endcode* (line

picoChip Designs Ltd. Page 6 of 24

68) tags. The C or ASM code for each AE is contained within a picoVHDL wrapper which defines the ports and the type of AE used amongst other things. In section 5.2, line 36 (*begin MEM*) tells us that this code is targeted at a MEM type AE.

NOTE: The MAC, STAN, MEM, CTRL and ANY AE types are also supported on the PC102 for backwards compatibility with the PC101. Where an AE code body does not use any of the additional features which are specific to the PC102, using these AE types allows the s/w to run on both the PC101 and PC102.

### 3.2 picoBus Switching Fabric

The picoBus is the name given to the switching fabric running vertically and horizontally between the processing elements in the array. Signals (between AEs) are assigned 32-bit slots on the picoBus at compile time thereby removing the need for arbitration and making performance completely deterministic.

Each AE communicates over the picoBus via its ports. These are defined using picoVHDL. Each AE has a number of ports which can be configured to be read (incoming) or write (outgoing). Lines 28-31 in section 5.2 provide an example. Data sent between AEs is:

- written to a write port FIFO (by the sending AE),

- sent over the picoBus on the next available slot and

- read from the read port FIFO (by the receiving AE).

By default, communication between AEs is data blocking. On attempting to read data from the picoBus, an AE will block until data becomes available in the read port FIFO. Similarly, when attempting to write data to the picoBus, the sending AE will block if its write port FIFO is full. A full write port FIFO infers that the receiving AE's read port is not taking data (i.e. is full itself).

Bandwidth on the picoBus between communicating AEs is assigned via @-rates. A signal is assigned an @-rate which is a power of 2, e.g. @8, @16. The @-rate is defined in the port declarations in both the sending and receiving AEs (see lines 29-31 in section 5.2). This @-rate is relative to the system clock (160MHz) and indicates how often data may be sent. For example, @8 means that a 32-bit quantity can be sent every 8 cycles (of the 160MHz bus). The receiving AE(s) must therefore issue a read (against the associated port) at least once every 8 cycles in order to prevent the sending AE from blocking.

picoChip Designs Ltd. Page 7 of 24

# 4 Uplink Preamble Detection on the picoArray<sup>™</sup>

The picoArray<sup>TM</sup> architecture enables parallelisms within an algorithm to be exploited, resulting in a level of performance associated with FPGA/ASICs whilst maintaining all the benefits associated with a software development environment.

This section describes a PC102 picoArray<sup>™</sup> implementation of a BS receiver synchronization block for the WirelessMAN-OFDM uplink. Coarse symbol timing is extracted from the received signal samples. The implementation is validated against a simple MATLAB model. The resource and performance characteristics for the implemented block are summarized below. A full source listing for the block is given in section 5.

| Input                     | ≤10 Msps, 16+j16 |

|---------------------------|------------------|

| AE Resources <sup>1</sup> | 3 MEM, 2 STAN2   |

<sup>&</sup>lt;sup>1</sup> The MEM AE type is used as no PC102 specific features are required.

Table 3 - PC102 OFDM Rx Synchronization

#### 4.1 Preamble Detection

As discussed in section 2.2, the coarse symbol timing can be determined from the data preamble used in the OFDM PHY uplink. Rather than calculating v(k) as in Equation 2, v(k) is calculated from the magnitude squared values of the two correlation values as shown in Equation 3. This avoids having to calculate the magnitude of the complex value P(k).

Equation 3

$$v(k) = \frac{\left|P(k)\right|^2}{\left|E(k)\right|^2}$$

The coarse symbol timing is determined from the per-sample value of v(k) as follows:

- a) As v(k) goes above a threshold value, a counter is started and incremented per sample.

- b) The counter continues until v(k) drops below the threshold value for 5 consecutive samples.

- c) Once the counter is stopped, it is compared against a threshold value (64). If greater or equal to this threshold value, a preamble symbol is deemed to have been received.

- d) The symbol start is calculated as being ¼ of the way between the counter start and stop samples. This should mean the symbol timing errs towards an early start to the symbol (i.e. within the CP).

The values for P(k) and E(k), as used in Equation 3, are calculated iteratively as follows:

$$P(k) = P(k-1) + (r^*(k) \times r(k-128)) - (r^*(k-128) \times r(k-256))$$

$$E(k) = E(k-1) + (r^*(k) \times r(k)) - (r^*(k-256) \times r(k-256))$$

picoChip Designs Ltd. Page 8 of 24

From the above, it becomes apparent that a certain amount of buffering is required:

- The received samples, r(k), need to be buffered in order to supply the delayed (by ½ OFDM symbol) samples for calculating P(k). The received samples also need to be buffered due to the processing delay in determining coarse symbol timing.

- The per-sample values used in the iterative calculations for P(k) and E(k) are buffered to avoid having to recalculate them.

- The values of P(k) need to be buffered for the period that v(k) is above the detection threshold.

Once coarse symbol timing is determined, the fractional frequency offset can be determined from the appropriate P(k).

## 4.2 picoArray<sup>™</sup> Implementation

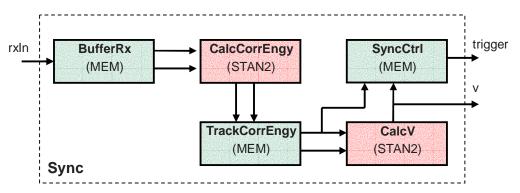

The picoArray<sup>™</sup> PC102 implementation for the receiver synchronization block is organized as a top-level structural entity and a number of AE code entities. This is illustrated in Figure 2.

The top-level structural entity (*Sync*, section 5.1) uses picoVHDL to 'wire' the various AE code entities together. The structural entity effectively encapsulates the AE code entities contained within it and defines an external interface through which the block is used. The structural entity (*Sync*) may then be instantiated one or more times at a higher-level within the overall design.

Figure 2 - 'Sync' structural entity

Each AE code entity in Figure 2 runs concurrently and synchronously with respect to the system clock (160MHz). In order to perform at upto 10Msps, the per-sample signals between the AEs need to be @16 or faster (e.g. @8). Each AE must also perform its per-sample processing in 16 cycles or less. The AE code entities are described in more detail in Table 4.

From the AE entity descriptions in Table 4, the CalcV entity is the limiting factor with taking 15 cycles per sample. To increase the performance significantly above 10Msps, the processing in CalcV could be split between two AEs, each taking <<15 cycles to process each sample. This is an example of the deterministic scalable performance offered by the picoArray<sup>TM</sup> – performance is increased by pipelining and exploiting parallelisms within an algorithm.

The CalcCorrEngy, TrackCorrEngy and CalcV entities could be left running for each and every received sample without any impact on the performance of other algorithms running on the

picoChip Designs Ltd. Page 9 of 24

picoArray<sup>TM</sup>. Alternatively, control could be added to the *RxBuffer* entity which would cause samples to be sent only when synchronization is being sought. This would cause the *CalcCorrEngy*, *TrackCorrEngy* and *CalcV* entities to block, resulting in a power saving. With only 8 cycles currently in the core loop of *RxBuffer*, this control logic could easily be added without impacting the target 10Msps performance.

| AE Code Body  | Description                                                                               |

|---------------|-------------------------------------------------------------------------------------------|

| BufferRx      | The incoming signal samples are buffered in memory. A MEM AE is used so                   |

|               | that several OFDM symbols worth of samples may be buffered to account for the             |

|               | overall processing delay of the synchronization block.                                    |

|               | The current and delayed (buffered) samples are reduced to 8+j8 and then sent              |

|               | to the CalcCorrEngy AE.                                                                   |

|               | The code body (lines 58-68, section 5.2) uses 8 cycles in its per-sample loop.            |

|               | As such, BufferRx could either cope with a faster sample rate or additional               |

|               | functionality could be added (see section 4.3).                                           |

| CalcCorrEngy  | The current and delayed signal samples (8+j8) are taken as inputs and the                 |

|               | values for $r(k)r(k)$ and $r(k)r(k-128)$ generated as outputs. Use of multiply-           |

|               | accumulate instructions necessitate the use of a STAN2.                                   |

|               | The code body (lines 58-70, section 5.3) uses 10 cycles in its core loop.                 |

| TrackCorrEngy | The per-sample outputs from CalcCorrEngy are taken and buffered. These                    |

|               | values are used to iteratively calculate the running totals for $P(k)$ and $E(k)$ .       |

|               | These totals are output on a per-sample basis. The buffers for $P(k)$ and $E(k)$          |

|               | necessitate the use of a MEM.                                                             |

|               | The code body (lines 63-89, section 5.6) has 12 cycles in its core loop.                  |

| CalcV         | The per-sample (32-bit) values for $P(k)$ and $E(k)$ are taken as inputs. $E(k)$ and      |

|               | P(k) are reduced to 16-bit values. A lookup table is used to approximate the              |

|               | division of $P(k)$ by $E(k)$ . A 32-bit value for $v$ is generated as an output on a per- |

|               | sample basis. Use of multiply-accumulate instructions necessitate the use of a            |

|               | STAN2.                                                                                    |

|               | The code body (lines 93-131, section 5.4) has 15 cycles in its core loop                  |

|               | (irrespective of the branches taken).                                                     |

| SyncCtrl      | The per-sample values for $v(k)$ and $P(k)$ are taken as inputs. The detection            |

|               | algorithm detailed above is used to extract the coarse symbol timing. The                 |

|               | values for $P(k)$ are buffered so that the fractional frequency offset can be             |

|               | calculated (not actually performed). The amount of buffering necessitates the             |

|               | use of a MEM.                                                                             |

|               | The code body (lines 65-92, section 5.5) contains 10 cycles in the per-sample             |

|               | processing loop until the point at which a preamble symbol is deemed to have              |

|               | been received.                                                                            |

Table 4 - Entities within 'Sync'

## 4.3 A Complete Synchronization Block

The source code presented in section 5 and described above implements the extraction of coarse symbol timing for the OFDM PHY uplink. Full receiver synchronization also involves detecting frequency offsets and making fine timing adjustments as determined from frequency-domain

picoChip Designs Ltd. Page 10 of 24

processing. Frequency offset correction is assumed to be performed by a separate NCO and complex multiplier.

As mentioned in the previous section, additional control logic could be added to the *RxBuffer* entity without affecting the 10Msps performance target. The additional control logic could be used to:

- Send samples to the *CalcCorrEngy*, *TrackCorrEngy* and *CalcV* entities only when burst synchronization is being sought.

- Remove the CP and output the OFDM symbol samples to the next block in the receiver chain (the frequency offset correction block).

- Apply fine timing adjustments as directed.

With being implemented on a MEM, the code and data memory available should easily be enough for the above additional tasks.

Similarly, the SyncCtrl entity is also significantly under-utilized. Calculating the fractional frequency offset could be performed in this AE – indeed, that's why the P(k) values are buffered in the current implementation.

#### 4.4 Test Results

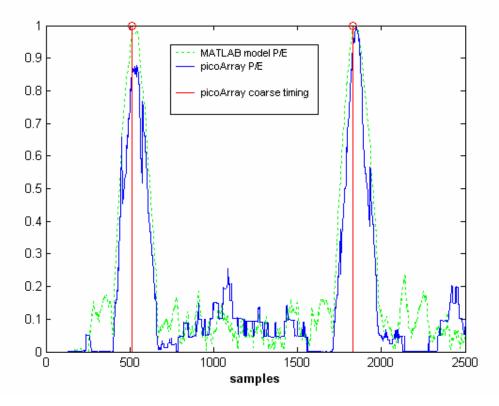

The PC102 implementation described in this application note was run in the cycle-accurate picoTools simulator to verify its functionality. The test vectors and results are read from and written to file by the simulator. The results where compared against a simple MATLAB model of the algorithm presented in section 4.1. The normalized results from both the picoArray<sup>TM</sup> implementation and the MATLAB model are shown in Figure 3.

Figure 3 - picoArray preamble detection vs MATLAB model

picoChip Designs Ltd. Page 11 of 24

The test inputs used for both the picoArray TM implementation and MATLAB model consisted of:

- 1x sampled data

- 20-tap channel filter for simulating multipath

- 1/8 CP (32 samples)

- Preamble symbols interspersed by data symbols

- Rx ADC sampling jitter

The red line in Figure 3 indicates the coarse symbol timing determined by the  $picoArray^{TM}$  implementation.

picoChip Designs Ltd. Page 12 of 24

### 5 Appendix: Source Code

#### 5.1 Sync

```

2

-- Sync

3

______

5

-- Copyright (c) 2003 picoChip Designs Ltd.

6

-- Proprietary and Confidential Information.

-- Not to be copied or distributed.

8

10

-- Description:

11

12

--* @short Structural entity for sync block

13

__*

14

--* The structural entity uses picoVHDL to wire the functional entities

--* together.

15

16

--*

--* @port rxIn received sample

--* @port v pre sample value for v (correlation^2/energy^2)

--* @port trigger signal sent when preamble detected

17

18

19

20

21

22

use work.all;

23

24

entity Sync is

25

generic(

26

bitwidth : integer);

27

port(

28

rxIn : in complex16@16;

v : out integer32@16;

29

30

trigger : out integer16pair@16);

31

end entity Sync;

32

33

architecture STRUCTURAL of Sync is

34

35

signal rxDel : complex16@16;

36

signal rxCur : complex16@16;

signal corr : complex16@16;

37

38

signal engy : complex16@16;

39

signal corrTotal : complex16@16;

signal engyTotal : complex16@16;

40

41

42

begin

43

44

bufRx : entity BufferRx

45

generic map (

46

bitwidth

=> bitwidth )

47

port map (

48

rxIn => rxIn,

rxDel => rxDel,

49

50

rxCur

=> rxCur );

51

52

trackPreamble : entity TrackCorrEngy

port map (

54

=> corr,

corr

=> engy,

55

engy

corrTotal => corrTotal,

engyTotal => engyTotal );

56

57

58

59

calcPreamble : entity CalcCorrEngy

60

port map (

61

rxDel => rxDel,

```

picoChip Designs Ltd. Page 13 of 24

```

62

rxCur => rxCur,

63

corr => corr,

engy => engy );

64

65

66

calcPoverE : entity CalcV

67

port map (

corrTotal => corrTotal,

engyTotal => engyTotal,

v => v);

68

69

70

71

72

73

74

preambleSync : entity SyncCtrl

port map (

v => v,

75

76

corrTotal => corrTotal,

trigger => trigger );

77

78

end Sync;

```

picoChip Designs Ltd. Page 14 of 24

#### 5.2 BufferRx

```

2

3

4

5

-- Copyright (c) 2003 picoChip Designs Ltd.

6

-- Proprietary and Confidential Information.

-- Not to be copied or distributed.

8

10

-- Description:

11

12

--* @short Buffer (filtered) receive samples.

13

_-*

14

--* After filtering, the receive samples are buffered in order to perform

15

--* preamble detection.

--*

16

17

--* @generic bitwidth bitwidth of received samples (eg. 10 if 10+j10)

18

_-*

19

--* @port rxIn

Received samples to be buffered

--* @port rxDel Delayed sample, 1/2 an OFDM symbol behind Current received sample

20

21

__*****************************

22

23

24

25

entity BufferRx is

26

generic(

27

bitwidth : integer);

28

port(

29

: in complex16@16;

rxIn

30

rxDel : out complex16@16;

rxCur : out complex16@16);

31

32

end entity BufferRx;

33

34

architecture ASM of BufferRx is

35

36

begin MEM -- Uses a MEMORY AE

37

38

-- Buffer 3 symbols worth (at 1x) plus CPs

39

initialize memory 0 : array(0 to 1023) of integer32 := (others => 0);

40

41

-- Initialisation of Registers to zero (apart from delayed sample index)

42

initialize regs := (0,0,128,0,0,0,0,0,0,0,0,0,0,0);

43

44

--Register Definitions.

register rxPtr is r0; -- Byte address for base of received sample buffer register rxDelIdx is r1; -- Index into buffer for delayed sample (1/2 sym)

45

46

47

register rxCurIdx is r2; -- Index into buffer for current sample

register rxCurRe is r4; -- Current sample (real part) register rxCurIm is r5; -- Current sample (imag part) register rxDelRe is r6; -- Delayed sample (real part) register rxDelIm is r7; -- Delayed sample (imag part)

48

49

50

-- Delayed sample (imag part)

51

register rxNormRe is r8; -- Normalized (to 8+j8) sample (real part)

52

53

register rxNormIm is r9; -- Normalized (to 8+j8) sample (imag part)

54

55

56

get rxIn,[rxCurIm:rxCurRe]

57

58

top:

59

lsl.0 rxDelIdx,2,rxPtr

60

add.0 rxDelIdx,1,rxDelIdx

\ ldl (rxPtr)0,[rxDelIm:rxDelRe]

61

asr.0 rxCurIm,bitwidth-8,rxNormIm \ asr.1 rxCurRe,bitwidth-8,rxNormRe

62

63

asr.0 rxDelIm,bitwidth-8,rxNormIm \ asr.1 rxDelRe,bitwidth-8,rxNormRe

64

lsl.0 rxCurIdx,2,rxPtr

add.0 rxCurIdx,1,rxCurIdx

\ put [rxNormIm:rxNormRe],rxDel

65

\ stl [rxCurIm:rxCurRe],(rxPtr)0 \ bra top

=-> and.0 rxCurldx,1023,rxCurldx \ get rxIn,[rxCurlm:rxCurRe]

66

```

picoChip Designs Ltd. Page 15 of 24

67 68 69

endcode;

end BufferRx;

picoChip Designs Ltd. Page 16 of 24

## 5.3 CalcCorrEngy

```

2

-- CalcCorrEngy

3

4

5

-- Copyright (c) 2003 picoChip Designs Ltd.

6

-- Proprietary and Confidential Information.

-- Not to be copied or distributed.

8

10

-- Description:

11

12

--* @short Calculate correlation and energy values for sample.

13

__*

14

--* The correlation is defined as (a-jb)(c+jd), where (a+jb) is the current

15

--* sample and (c+jb) is the delayed sample.

16

\mbox{--*}\mbox{ }\mbox{\sc NOTE:} The conjugate of the current sample is used in the correlation.

17

18

--* The energy is defined as (a+jb)(a-jb).

19

__*

20

--* The delayed and current sample bitwidth <=8

21

__*

22

_-*

@port rxDel Delayed sample

23

--* @port rxCur Current sample

--* @port corr Correlation va

24

Correlation value (complex)

--* @port engy Energy value (real)

25

__***********

26

*********

27

28

--/

29

entity CalcCorrEngy is

30

port(

31

rxDel: in complex16@16;

32

rxCur : in complex16@16;

33

corr : out complex16@16;

34

engy : out complex16@16);

35

end entity CalcCorrEngy;

36

37

architecture ASM of CalcCorrEngy is

38

39

begin STAN2 -- Uses a STAN2 AE

40

41

-- Initialisation of Registers to zero

42

initialize regs := (0 to 14 => 0);

43

44

--Register Definitions.

register rxDelRe is r0; -- Delayed sample for correlation (real) register rxDelIm is r1; -- Delayed sample for correlation (imag)

45

46

is r2; -- Current sample (real)

47

register rxCurRe

48

register rxCurIm

is r3; -- Current sample (imag)

register corrRe is r4;

register corrIm is r5;

register engyRe is r6;

register engyIm is r7;

49

-- correlation (real)

50

-- correlation (imag)

-- energy (real)

51

52

-- energy (imag=zero)

53

54

code

55

get rxCur,[rxCurIm:rxCurRe]

56

get rxDel,[rxDelIm:rxDelRe] \ mul rxCurRe,rxCurRe,acc0

57

58

top:

59

mac rxCurIm,rxCurIm,acc0

60

readacc acc0,frac,engyRe

61

\ mul rxCurRe,rxDelRe,acc0

put [engyIm:engyRe],engy

62

mac rxCurIm,rxDelIm,acc0 -- NB: Multiplying delayed by conjugate of current

63

readacc acc0,frac,corrRe

64

mul rxCurRe,rxDelIm,acc1

65

msub rxCurIm,rxDelRe,acc1 -- NB: Multiplying delayed by conjugate of current

66

readacc accl, frac, corrIm

```

picoChip Designs Ltd. Page 17 of 24

picoChip Designs Ltd. Page 18 of 24

#### 5.4 CalcV

```

2

3

4

5

-- Copyright (c) 2003 picoChip Designs Ltd.

-- Proprietary and Confidential Information.

-- Not to be copied or distributed.

8

10

-- Description:

11

12

--* @short Calculate V = correlation/energy.

13

__*

--* As the preamble consists of 2 repeating halfs (in the time domain),

14

15

--* 2*correlation/energy should approach 1 as the current sample reaches the

16

--* end of the preamble symbol.

17

18

--* This block approximates 2*correlation/energy by correlation^2/energy^2.

19

__*

The theoretical max value for correlation^2 is 1/4*energy^2.

20

_-*

21

__*

The energy total (squared) is normalized to the range 2^15 to 2^16-1.

22

The correlation total (squared) is normalized by shift by the same number

23

of bits minus 2 (given the max value is 1/4 of energy^2).

24

__*

--* A lookup table is used to perform the division. The energy^2 value is

26

__*

reduced to 8 bits (bottom 2 bits = 0) to form an index into the table.

27

__*

28

--* At the point of detection correlation^2 should approach energy^2 (due to

29

__*

effective multipication by 4 in the shifting above).

30

Therefore, taking energy=2^16-1 as an example, the last entry in the

31

division LUT is used, giving a result of 2^16-1 * 8224 = 5.39e8.

32

__*

v should approach 5.39e8 at the point of detection for all values of

33

energy.

34

__*

35

--* A 32-bit value for v is returned.

--*

36

37

--* @port corrTotal Correlation total (summed over half OFDM symbol)

38

--* @port engyTotal Energy total(summed over 1 OFDM symbol)

--* @port v

39

correlation^2/energy^2

__********

40

41

--/

42

entity CalcV is

43

port(

44

corrTotal : in complex16@16;

45

engyTotal : in complex16@16;

v : out integer32@16);

46

47

end entity CalcV;

48

49

architecture ASM of CalcV is

50

51

begin STAN2

52

53

-- Lookup table for dividing in the range 1/128 to 1/255

54

initialize memory 0 : array(0 to 127) of integer16 := (

55

16384, 16257, 16132, 16009, 15888, 15768, 15650, 15534,

56

15420, 15308, 15197, 15087, 14980, 14873, 14769, 14665,

57

14564,14463,14364,14266,14170,14075,13981,13888,

58

13797, 13707, 13618, 13530, 13443, 13358, 13273, 13190,

59

13107, 13026, 12945, 12866, 12788, 12710, 12633, 12558,

60

12483,12409,12336,12264,12193,12122,12053,11984,

61

11916,11848,11782,11716,11651,11586,11523,11460,

62

11398, 11336, 11275, 11215, 11155, 11096, 11038, 10980,

63

10923, 10866, 10810, 10755, 10700, 10645, 10592, 10538,

64

10486,10434,10382,10331,10280,10230,10180,10131,

65

10082,10034,9986,9939,9892,9846,9800,9754,

66

9709,9664,9620,9576,9533,9489,9447,9404,

```

picoChip Designs Ltd. Page 19 of 24

```

67

9362,9321,9279,9239,9198,9158,9118,9079,

68

9039,9001,8962,8924,8886,8849,8812,8775,

69

8738,8702,8666,8630,8595,8560,8525,8490,

70

8456,8422,8389,8355,8322,8289,8257,8224

71

72

73

-- Initialisation of Registers to zero

74

initialize regs := (0 to 14 => 0);

75

76

--Register Definitions.

77

register corrRe is r0; -- correlation (real)

register corrIm is r1; -- correlation (imag) register engyRe is r2; -- energy (real) register engyIm is r3; -- energy (imag=zero)

78

79

80

81

register corr2Lo

is r4; -- correlation squared (lower 16-bits)

register corr2Lo is r4; -- correlation squared (lower 16-bits) register corr2Hi is r5; -- correlation squared (upper 16-bits) register engy2Lo is r6; -- energy squared (lower 16-bits) register engy2Hi is r7; -- energy squared (upper 16-bits) register signBits is r8; -- num of (redundant) sign bits in energy register dataBits is r9; -- number of data bits

82

83

84

85

86

87

register msbIsData is r10; -- MSB in lower 16-bits is data (and not sign)

register divIdx is r11; -- Index into division LUT register vLo is r12; -- v (lower 16-bits) register vHi is r13; -- v (upper 16-bits)

88

89

90

register value is r13; -- v (upper 10-bits)

register xfactor is r14; -- multiplication factor from division LUT

91

92

93

code

94

get engyTotal,[engyIm:engyRe]

95

mul engyRe, engyRe, acc0

96

97

top:

98

get corrTotal,[corrIm:corrRe] \ readacc32 acc0,[engy2Hi:engy2Lo]

99

sbc engy2Hi,signBits \ mul corrRe,corrRe,acc0

100

sub.0 signBits,15,r15 \ mac corrIm,corrIm,acc0

101

lsr.0 engy2Lo,15,msbIsData \ beq lowerBitsOnly

102

=-> readacc32 acc0,[corr2Hi:corr2Lo]

103

104

upperBits:

105

-- Energy contains significant bits in upper 16-bit word

106

-- Shift so that MSB is bit14 (0 to 15) of lower 16-bit word

lsl.0 engy2Hi,signBits,engy2Hi \ sub.1 16,signBits,dataBits

107

108

lsr.0 engy2Lo,dataBits,engy2Lo \ lsl.1 corr2Hi,2,corr2Hi

109

lsl.0 corr2Hi,signBits,corr2Hi \ or.1 engy2Hi,engy2Lo,engy2Lo

110

and.0 [lsr engy2Lo,7],16#fc#,divIdx \ lsr.1 corr2Lo,2,corr2Lo

111

lsr.0 corr2Lo,dataBits,corr2Lo \ ldw (divIdx)0,xfactor \ bra compare

112

=-> or.0 corr2Hi,corr2Lo,corr2Lo

113

114

lowerBitsOnly:

115

-- Energy only contains significant bits in lower 16-bit work

116

-- Shift so that MSB is bit14 (0 to 15) of lower 16-bit word

117

lsr.0 engy2Lo, msbIsData, engy2Lo

118

sbc engy2Lo,signBits

119

lsl.0 engy2Lo,signBits,engy2Lo

120

and.0 [lsr engy2Lo,7],16#fc#,divIdx \ lsl.1 corr2Lo,2,corr2Lo

121

lsr.0 corr2Lo,msbIsData,corr2Lo \ ldw (divIdx)0,xfactor \ bra compare

122

=-> lsl.0 corr2Lo, signBits, corr2Lo

123

124

compare:

125

-- MSB of energy should be after sign bit

126

mul corr2Lo,xfactor,acc0

127

readacc32 acc0,[vHi:vLo]

128

put [vHi:vLo], v \ get engyTotal,[engyIm:engyRe] \ bra top

129

=-> mul engyRe,engyRe,acc0

130

131

endcode;

132

end CalcV;

```

picoChip Designs Ltd. Page 20 of 24

#### 5.5 SyncCtrl

66

```

2

-- SyncCtrl

3

______

4

5

-- Copyright (c) 2003 picoChip Designs Ltd.

-- Proprietary and Confidential Information.

-- Not to be copied or distributed.

8

10

-- Description:

11

__***********************************

12

--* @short Synchronization control

13

__*

14

--* Coarse symbol timing is determined for the value for v (1 per rx sample).

15

--* Coarse timing is calculated by waiting for v to go above the threshold

16

--* value for a certain number of samples. As v falls back down below the

17

threshold then the coarse sample timing is taken as 1/4 of period

18

--* v was above the threshold.

19

__*

20

--* Once coarse timing has been calculated, the initial fractional frequency

21

--* offset can be detemined (not done here).

22

_-*

23

--* @port v

Approximation of 2*correlation/energy

--* @port corrTotal Running correlation total (per sample)

24

25

--* @port trigger Trigger when coarse timing determined

26

__**********************************

27

--/

28

entity SyncCtrl is

29

port(

30

: in integer32@16;

31

corrTotal : in complex16@16;

32

trigger : out integer16pair@16);

33

end entity SyncCtrl;

34

35

architecture ASM of SyncCtrl is

36

37

-- Threshold level taken from upper 16-bits of v.

38

constant VLEVEL : integer := 16#0800#;

39

-- Min number of samples needed above detection level for sync

40

constant VABOVE : integer := 64;

41

-- Number of samples v is allowed to dip below level without resetting

42

constant VBELOW : integer := 5;

43

44

begin MEM

45

46

-- Buffer correlation totals

47

initialize memory 0 : array(0 to 256) of integer32 := (others => 0);

48

49

-- Initialisation of Registers to zero

50

initialize regs := (0 to 14 => 0);

51

52

--Register Definitions.

53

register vLo is r0; -- v (lower 16-bits)

register vHi is r1; -- v (upper 16-bits)

register corrTotalRe is r2; -- running correlation total (real)

register corrTotalIm is r3; -- running correlation total (imag)

54

register vHi

55

56

register corrPtr is r4; -- pointer into correlation buffer register belowCtr is r5; -- number of consecutive samples below threshold register nDetect is r6; -- number of samples detected above threshold register nSamples is r7; -- number of samples processed register triggerLo is r8; -- sample number corresponding to the point

57

58

59

60

61

is r8; -- sample number corresponding to the point of

62

detection

63

register triggerHi

is r9; -- not used

64

65

code

```

picoChip Designs Ltd. Page 21 of 24

```

67

top:

68

add.0 nSamples,1,nSamples \ get v,[vHi:vLo]

69

sub.0 vHi,VLEVEL,r15 \ get corrTotal,[corrTotalIm:corrTotalRe]

70

stl [corrTotalIm:corrTotalRe],(corrPtr)0 \ blt below -- branch if below level

71

=-> sub.0 [lsr corrPtr,2],0,r15

72

73

above:

74

copy.0 0,belowCtr \ bra top

75

=-> add.1 corrPtr,4,corrPtr

76

77

below:

78

add.0 belowCtr,1,belowCtr \ beq top -- branch if no recent samples above level

79

=-> sub.0 belowCtr, VBELOW, r15

80

blt top -- branch if still within limit of samples below level

81

=-> sub.0 [lsr corrPtr,2], VABOVE, r15

82

sub.0 [lsr corrPtr,2], VBELOW, nDetect \ blt top -- branch if not enough samples

83

=-> copy.0 0,corrPtr

84

85

detect:

86

-- We've detected enough samples above the level, work out coarse timing

87

\verb|sub.0| nSamples, \verb|nDetect|, triggerLo| \setminus lsr.1| nDetect|, 2, \verb|nDetect|

88

add.0 triggerLo,nDetect,triggerLo \ bra top

89

=-> put [triggerHi:triggerLo],trigger

90

91

92

endcode;

93

end SyncCtrl;

```

picoChip Designs Ltd. Page 22 of 24

## 5.6 TrackCorrEngy

```

2

-- TrackCorrEngy

3

______

4

5

-- Copyright (c) 2003 picoChip Designs Ltd.

-- Proprietary and Confidential Information.

-- Not to be copied or distributed.

8

10

-- Description:

11

12

--* @short Keep running totals for correlation and energy over 1 OFDM symbol

13

__*

14

--* A running correlation total is kept for r'(n)*r(n-128) summed over half

15

--* an OFDM symbol (128 samples at 1x).

16

--* A running energy total is kept for r'(n)*r(n) summed over a full OFDM

17

symbol.

18

__*

19

\ensuremath{^{--*}} The per sample correlation and energy values are buffered. The totals

20

--* are calculated iteratively.

21

__*

per sample correlation value

22

--* @port corr

--* @port engy per sample energy value

--* @port corrTotal current total for correlation (over 1/2 OFDM symbol)

--* @port engy

23

24

25

--* @port engyTotal current total for energy (over 1 OFDM symbol)

26

__***********************************

27

28

entity TrackCorrEngy is

29

port(

30

: in complex16@16;

corr

: in complex16@16;

31

32

corrTotal : out complex16@16;

engyTotal : out complex16@16);

33

34

end entity TrackCorrEngy;

35

36

architecture ASM of TrackCorrEngy is

37

constant CORR_BASE : integer := 0;

constant ENGY_BASE : integer := 512;

38

39

40

41

begin MEM

42

43

initialize memory CORR_BASE : array(0 to 127) of integer32 := (others => 0);

initialize memory ENGY_BASE : array(0 to 255) of integer32 := (others => 0);

44

45

46

-- Initialisation of Registers to zero

47

initialize regs := (CORR_BASE,0,ENGY_BASE,0,0,0,0,0,0,0,0,0,0,0,0,0);

48

49

--Register Definitions.

register corrPtr is r0; -- pointer to entry in buffer of register corrIdx is r1; -- index into correlation buffer

50

-- pointer to entry in buffer of correlation values

51

register corrIdx is r1; -- index into correlation butter register engyPtr is r2; -- pointer to entry in buffer of energy values register engyIdx is r3; -- indx into energy buffer register corrRe is r4; -- per sample correlation value (real) register corrIm is r5; -- per sample correlation value (imag) register corrTotalRe is r6; -- correlation running total (real)

52

53

54

55

56

57

register corrTotalIm is r7; -- correlation running total (imag)

register engyRe is r8; -- per sample energy value (real) register engyIm is r9; -- per sample energy value (imag=0)

58

59

register engyTotalRe is r10; -- energy running total (real) register engyTotalIm is r11; -- energy running total (imag=0)

60

61

62

63

64

add.0 [lsl engyIdx,2],ENGY_BASE,engyPtr

65

66

top:

```

picoChip Designs Ltd. Page 23 of 24

```

67

-- For correlation and energy:

68

-- o Calculate pointer into buffer

69

o Read value from buffer - this is the oldest value

70

-- o Subtract oldest value from total

71

-- o Get latest per-sample value

o Add latest value to total

72

73

o Write latest value to buffer and advance index

74

75

add.0 [1sl corrIdx,2],CORR_BASE,corrPtr \ ldl (engyPtr)0,[engyIm:engyRe]

76

add.0 engyIdx,1,engyIdx \ ldl (corrPtr)0,[corrIm:corrRe]

77

add.0 corrIdx,1,corrIdx \ sub.1 engyTotalRe,engyRe,engyTotalRe

78

\verb"sub.0" corrTotalRe", \verb"corrTotalRe" \setminus \verb"sub.1" corrTotalIm", \verb"corrIm", \verb"corrTotalIm" |

79

and.0 engyIdx, 255, engyIdx \ get engy, [engyIm, engyRe]

80

asr.0 engyRe,6,engyRe \ asr.1 engyIm,6,engyIm

81

add.0 engyRe,engyTotalRe,engyTotalRe \ get corr,[corrIm,corrRe] \ put

82

[engyTotalIm:engyTotalRe],engyTotal

83

asr.0 corrRe,6,corrRe \setminus asr.1 corrIm,6,corrIm

84

add.0 corrRe,corrTotalRe,corrTotalRe \ add.1 corrIm,corrTotalIm

85

and.0 corrIdx,127,corrIdx \setminus put [corrTotalIm:corrTotalRe],corrTotal

86

stl [engyIm:engyRe],(engyPtr)0 \ bra top

87

=-> add.0 [lsl engyIdx,2],ENGY_BASE,engyPtr \ stl [corrIm:corrRe],(corrPtr)0

88

89

endcode;

90

end TrackCorrEngy;

```

picoChip Designs Ltd. Page 24 of 24