# FEATURES ☐ Complete 2400 bps modem and 9600/7200/4800/2400 bps Sendfax

- ☐ Single 5V supply with 10 mW power down mode

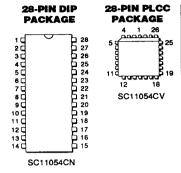

- ☐ Pin compatible with Sierra SC11024 2400 bps modem

- Compatible with CCITT V.29, V.27ter, V.22 bis, V.22, V.21, and BELL 212A and 103 standards

- ☐ Integrated DTMF/Guard tone generator, call progress monitor

## ☐ 2100/2225 Hz tone detector ☐ Contains an on-chip hybrid

- ☐ Analog, digital, and remote digital loopback

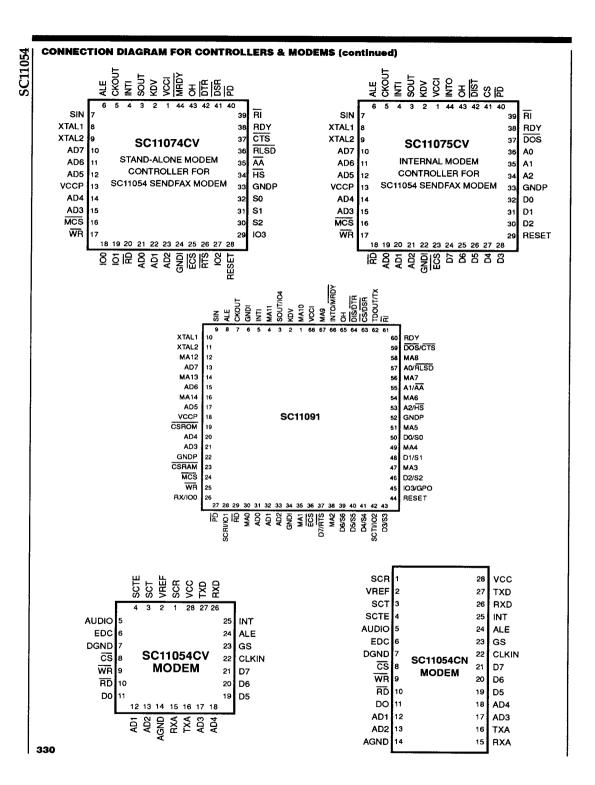

- Compatible with SC11011,

SC11021, SC11061, SC11074,

SC11075 and SC11091 controllers

- ☐ Programmable audio output

- ☐ CMOS technology☐ Synchronous & Asynchronous

modes

☐ EIA 2188 Class 2 compatible firmware available

#### GENERAL DESCRIPTION

The SC11054 is a complete 2400 bps, 5V only modem IC including a Sendfax capability up to 9600 bps. This IC contains all modem functions except the adaptive equalizer.

It is used in conjunction with an external controller, such as the Sierra SC11011 (for either parallel bus or RS-232 applications) and memory to implement a 2400 bps

full duplex modem, compatible with the CCITT V.22 bis recommendation, having Sendfax capability at 9600/7200 bps compatible with the V.29 recommendation or 4800/

## IMAGE UNAVAILABLE

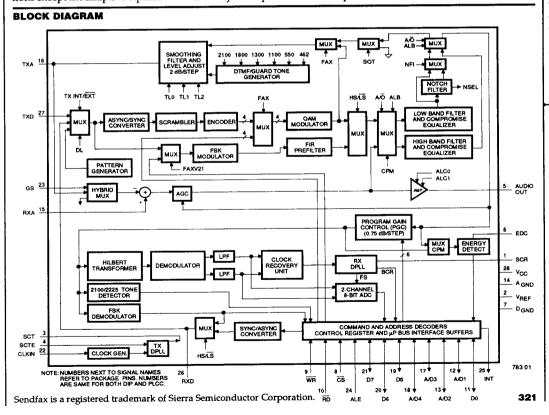

#### FUNCTIONAL DESCRIPTION OF THE SC11054 MODEM

The SC11054 includes the following (See Block Diagram, Figure 1):

- ☐ Full transmitter consisting of

- Async to Sync converter

- Scrambler

- Data encoder

- 75% square root of raised cosine pulse shaper in V.22 mode, 50/90% square root of raised cosine shaping in V.27 4800/2400 bps modes and 20% square root of raised cosine shaping in V.29 9600/7200 bps modes

- Quadrature amplitude and phase modulators

FSK (Bell 103 and CCITT V.21)

- FSK (Bell 103 and CCITT V.21) modulator

- Hybrid

- High band and low band filters

High band and low band compromise equalizers

- ☐ V.22 notch filter (selectable at 550 or 1800 Hz)

- ☐ Transmit smoothing filter

- ☐ Programmable attenuator for transmit level adjust

- DTMF, 462 Hz, 550 Hz, 1100 Hz, 1300 Hz, 1800 Hz, and 2100 Hz tone generator

- ☐ Tone detector for 2100/2225 Hz frequencies

- ☐ Transmit clock circuit for synchronous operation (slave, external, and internal modes)

- Pattern generator for generating fixed digital patterns in handshaking mode

- ☐ Receive section consisting of

- 64-step programmable gain controller (PGC)

- Energy detector at the output of the PGC

- Hilbert transformer

- Quadrature amplitude and phase demodulators (free running carrier) with low pass filters

- Baud timing recovery circuit (sampling clock of 600 Hz)

- FSK demodulator

- Sync to Async converter

- ☐ Two channel 8-bit analog to digital converter (ADC)

- ☐ Control and Status registers

☐ 8-bit microprocessor interface

with interrupt and multiplexed

address/data lines

- ☐ Audio output with level adjust

### Transmitter (V.22bis, V.22, 212A and V.21 and 103)

Since data terminals and computers may not have the timing accuracy required for 2400/1200 bps transmission (0.01%), timing correction on the incoming data stream must be made. The async/ sync converter accepts asynchronous serial data clocked at a rate between 2400/1200 Hz +2.3%, -2.5%. It outputs serial data at a fixed rate of 2400/1200 Hz ±0.01% derived from the master clock oscillator. To compensate for the input and output rate differences, a stop bit is either deleted or inserted when necessary. If the input data rate is slower than the output data rate, a stop bit is inserted. If the input data rate is faster than the output data rate, a stop bit is deleted. The output of the async/ sync converter is applied to the scrambler.

The scrambler is a 17-bit shift register clocked at 2400/1200 Hz. Outputs from the 14th and 17th stages are exclusive OR'd and further exclusive OR'd with the input data. The resultant data is applied to the D input of the shift register. Outputs from the first four/two stages of the shift register form the quad/dibit that is applied to the QAM/QPSK modulator. The purpose of the scrambler is to randomize data so that the energy of the modulated carrier is spread over the band of interest-either the high band, centered at 2400 Hz, or the low band, centered at 1200 Hz. In the 2400 bps mode, the modem actually sends four bits at a time, called a quadbit. The actual rate of transmission for a quadbit is 600 baud. This is the optimum rate of transmission over the general switched telephone network for a full duplex FDM (frequency division multiplexing) modem because band limit filters in the central office cut off at about 3000 Hz.

In the 2400 bps data rate, the data to be transmitted is divided into groups of four consecutive bits (quadbits). The first two bits of the quadbit are encoded as a phase quadrant change relative to the quadrant occupied by the preceding signal element. The last two bits define one of the four signaling elements associated with the new quadrant.

In the 1200 bps data rate, the data stream is divided into groups of two consecutive bits (dibits). The dibits are used to determine the phase quadrant change relative to the quadrant occupied by the preceding signal element. The resulting signaling elements from the inphase (I) and quadrature (Q) channels are passed through baseband filters with a square root of raised cosine shape. The filtered signals subsequently modulate sine and cosine carriers, and add to form the QAM/QPSK signal. The

monitor mode, the low-band filter is scaled down by a factor of 2.5 to center it over a frequency range of 300 to 660 Hz. Thus, during call establishment in the originate mode, call progress tones can be monitored through the scaled low-band filter and the modem answer tone or voice can be monitored through the unscaled high-band filter.

The low-band filter is a 10th order switched-capacitor band-pass filter with a center frequency of 1200 Hz. In the originate mode, this filter is used in the transmit direction; in the answer mode, it is used in the receive direction. When analog loopback is used in the originate mode, this filter, together with the low-band delay equalizer, is in the test loop.

The low-band delay equalizer is a 10th order switched-capacitor allpass filter that compensates for the group delay variation of the low-band filter and half of the compromise line characteristics, producing a flat delay response within the pass-band.

The high-band filter is a 10th order switched-capacitor band-pass filter with a center frequency of 2400 Hz. In the answer mode, this filter is used in the transmit direction; in the originate mode, it is used in the receive direction. When analog

loopback is used in the answer mode, this filter, together with the high-band delay delay equalizer, will be in the test loop.

The high-band delay equalizer is a 10th order switched-capacitor allpass filter that compensates for the group delay variation of the high-band filter and half of the compromise line characteristics, producing a flat delay response within the pass-band. The transmit smoothing filter is a second-order low-pass switched-capacitor filter that adds the modem transmit signal to the V.22 guard tones. It also provides a 2 dB per step programmable gain function to set the output level.

#### Transmitter (V.29 and V.27ter)

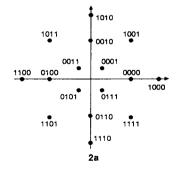

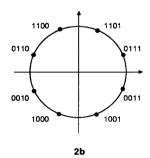

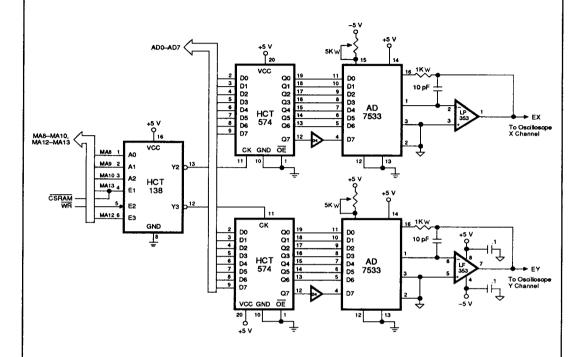

In these modes the functions required to convert the transmit data to transmit analog signal are partitioned between the analog and controller chips. The firmware implemented in the controller chip performs the scrambling and also generates the training sequences as required by the V.29 and V.27ter specifications. Next, it carries out the encoding function based on the selected mode and bit rate (9600/ 7200/4800/2400 bps) and determines the new location of the constellation point. A 4-bit word (a3 a2 a, a,) has been assigned to each constellation point to facilitate the quadrature modulation by the analog chip. (See figures 2a and b).

Every two baud periods (2400/1600/1200 bauds), the analog chip sends an interrupt to the controller, within 250 μs, the controller has to write an 8-bit word into the FAXR register of the analog chip, that conveys the constellation point locations for two consecutive bauds (8-bit word corresponds to 8-bits of Tx data in 9600 bps mode, 6 bits in 7200 bps mode, 6 bits in 4800 bps mode and 4 bits in 2400 bps mode).

The analog chip will perform quadrature modulation on the 4 LSB's first and 4 MSB's on the next baud period. It also caries out square root of raised cosine shaping based on the selected baud rate. In fax mode (V.29, V.27ter) the modulated signal will directly feed the transmit smoothing filter, bypassing the band pass filter and equalizer.

#### Transmitter (V.21 FAX)

In FAX mode (BR3=1 or BR2=1) the operation of V.21 modem, referred to as V.21FAX, is half-duplex and uses the high channel.

The input/output data will be handled through the controller interface instead of the TXD/RXD pins. When transmitting in V.21 mode, the analog chip sends interrupts to the controller at a 300 Hz ±.01% rate which serves as a timing base. Within 2 ms after every eight interrupts, the controller has to

Figure 1. 4-Bit Words (a<sub>3</sub>a<sub>2</sub>a<sub>1</sub>a<sub>0</sub>) Identifying Constellation Points in V.29 (2a) and V.27ter (2b)

write an 8-bit word into the FAXR register that corresponds to eight consecutive transmit data bits with the LSB to be sent first.

The analog chip will perform a parallel-to serial conversion on the 8-bit word and feed the result into the FSK modulator block. The signal path from FSK modulator input to TXA pin will be similar to the normal V.21 mode.

### Receiver (V.22 bis, V.22, 212A, V.21 and 103)

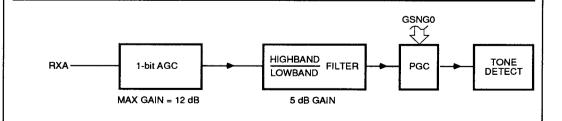

The receiver section consists of an energy detector, programmable gain control (PGC), part of the QAM/QPSK demodulator, FSK demodulator, 8-bit ADC and sync/async converter.

The received signal is routed through the appropriate band-pass filter and applied to the energy detector and PGC circuit. The energy detector provides detection within 17 to 24 msec. It is set to turn on when the signal exceeds -43 dBm and turn off when the signal falls below -48 dBm measured at the chip. A 2 dB minimum hysteresis is provided between the turn on and turn off levels. In call progress mode, the energy detector is connected to the output of the PGC to allow detection level adjustment.

The output of the receive filter is applied to the programmable gain control (PGC). This circuit has a wide overall range of 47.25 dB and provides 64 steps of 0.75 dB/step. The PGC gain is controlled by the external processor. It also provides auto-zeroing to minimize the output DC offset voltage.

The QAM/QPSK demodulator uses a coherent demodulation technique. Output of the programmable gain control (PGC) is applied to a Hilbert transformer that produces an in-phase and 90° out of phase component. These components are then demodulated to baseband in a mixer stage where

individual components are multiplied by a free-running carrier. The baseband components are lowpass filtered to produce I and Q (Inphase and Quadrature) channel outputs. The I and Q channel outputs are both filtered by 300 Hz band-pass filters. Then they are rectified, summed and passed through a band-pass filter giving a 600 Hz signal. This signal is applied to a digital phase lock loop (DPLL) to produce a baud rate clock. Using the recovered clock signal, the I and O channels are sampled and digitized into 8-bit samples by the ADC. Each channel (I and Q) is sampled twice during a baud period, once at the middle and once at the end of the baud period, allowing T/2 or T sampling operation. The external processor is interrupted once every baud period (1.667 msec). The processor should read the I and Q samples (within 100 µs from the time interrupt is issued), and perform adaptive equalization, carrier phase tracking, data decoding, and data descrambling. One quad/ dibit is transferred from the SC11054 during each baud period.

In the asynchronous mode, data received from the processor is applied to the sync/async converter to reconstruct the originally transmitted asynchronous data. For data which had stop bits deleted at the transmitter (overspeed data), these stop bits are re-inserted. Underspeed data is passed essentially unchanged. The sync/async converter has two modes of operation. In the basic signaling mode, the buffer can accept an overspeed which corresponds to one missing stop bit in eight characters. The length of the start bit and data elements will be the same, and the stop bit will be reduced by 12.5%. In the extended-signaling range, the buffer can accept one missing stop bit in four characters and the stop bits will be reduced by 25% to allow for overspeed in the transmitting terminal. Output of the sync/async converter, along with the output of the FSK demodulator, is applied to a multiplexer. The multiplexer selects the appropriate output, depending on the operating speed and output data received on the RXD pin.

For low-speed operation, the FSK demodulator is used. The output of the PGC amplifier is passed through a zero crossing detector and applied to a counter that is reset on zero crossings. The counter is designed to cycle at a rate 4 times faster than the carrier signal. The counter output is low-pass filtered and hard limited to generate FSK data.

To improve the performance of the receiver at low signal levels, while maintaining a wide amplitude range, a 1-bit AGC circuit is placed prior to the band-pass filter. The decision thresholds of this AGC are controlled by the AGCVT bit. When AGCVT = 1, the thresholds will be 6 dB further apart than when AGCVT = 0, so that the probability of gain change will be reduced. The status of the AGC gain is available through the AGCO bit. AGC will have 8 dB more gain when AGCO = 1. Status of AGCO should be monitored at every baud timing period and when it makes a transition (causing a gain-hit) the PGC's gain shouldbe modified accordingly to prevent divergence of the adaptive equalizer.

#### Receiver (V.21 FAX)

When receiving in V.21FAX mode, which is half-duplex, the serial output data from FSK demodulator will be loaded into a serial-to-parallel register. The timing for serial shift as well as interrupt is derived from the received data through a resettable counter. The counter divides an input clock of 9.6 kHz by 32 to generate a 300 Hz signal. On every high to low transition of data the counter is reset and resynchronized to data timing. Assuming a received bit rate of 300 BPS ±0.01%, the interrupt should have an aver-

age frequency of 300 Hz ±.01%. The controller should count the interrupt pulses and read the contents of FAXV21R register within 1.5 ms after every eighth pulse. The LSB corresponds to FSK demodulator output that has been received first in time.

A flag detector is implemented on the chip to facilitate detection of flag sequences (Hex 7E) in V.21 FAX mode. The decoder, detects the flag itself or possible rotations of it; i.e. it detects 01111110. 00111111, 1001111, 11001111, 11100111, 11110011, 11111100. If any of these combinations is detected, then FLAGDET bit of the status register will go high and stay high until the condition goes away. The flag detector output is updated on every interrupt pulse in the V.21FAX receive mode. To ensure that the flag detector is not triggered by false data, it is recommended that the FLAGDET bit be checked for at least 16 consectutive interrupts after this bit gets set. If it does not stay high continuously the received data may not be a true flag sequence. Flag detector should be used in V.21FAX receive mode only.

#### **Tone Detector**

A digital tone detector has been implemented in the SC11054 to facilitate detection of 2100/2225 Hz tones. The output of the PGC is passed through a zero crossing detector which in turn feeds a digital timer that verifies the period of the tone. If four consecutive periods of input tone pass the requirements, then, the appropriate tone detector output (TD2100 or TD2225 bit in status register) goes high. To detect these tones user must insert the highband filter in the receive path to allow their passage, also, PGC gain must be set properly to amplify the input to the tone detector. It will be a good practice to monitor ED bit when reading TD to ensure that the signal energy is within acceptable limits.

With the PGC gain word (PGCR) set to 011111 the tone detector threshold will be typically -43dBm.

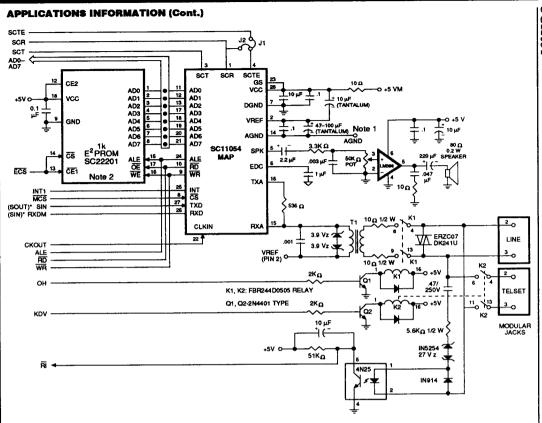

#### Hybrid

The signal on the phone line is the sum of the transmit and receive signals. The hybrid subtracts the transmitted signal from the signal on the line to form the received signal. It is important to match the hybrid impedance as closely as possible to the telephone line to produce only the received signal. When the internal hybrid is used, by turning the "Hybrid" code on through the interface, this matching is provided by an external resistor connected between the TXA and RXA pins on the SC11054. The filter section provides sufficient attenuation of the out-of-band signals to eliminate leftover transmit signals from the received signal. The hybrid also acts as a first order low-pass antialiasing filter. The hybrid can be deactivated by the controller.

The SC11054 internal hybrid is intended to simplify the phone line interface. The internal hybrid can compensate for the loss in the line coupling transformer used in the DAA. By tying the GS pin to AGND, V<sub>REF</sub> or V<sub>CC</sub> compensation levels of 0, +2, +3 dB, respectively are provided.

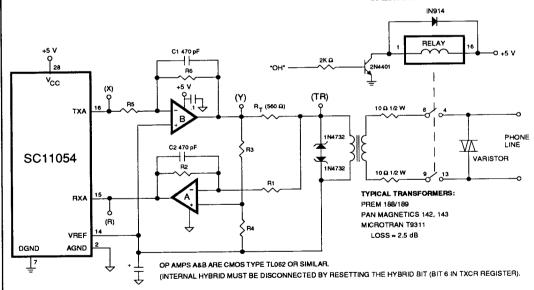

With a higher loss transformer, some degradation in performance at lower signal levels will occur. Specifically, the bit error rate, when operating at receive signal levels below -40 dBm in the presence of noise, will be higher. The energy detect on/off levels measured at the line will also be different from those specified at the chip. An external hybrid circuit, shown in Figure 2, can be used to overcome these losses and achieve maximum performance. In this case, the internal hybrid must be turned off by setting bit 6 of the TXCR register to 0.

The external hybrid circuit uses two

operational amplifiers, one in the transmit path and the other in the receive path. The SC11054 internal transmit stage provides a gain of 6 dB over the transmit signal level desired at the line. Under ideal conditions, with no loss in the transformer and perfect line matching, the signal level at the line will then be the desired value. In practice, however, there is impedance mismatch and a loss in the coupling transformer. Therefore, it may be desired to provide a gain in the transmit and receive paths to overcome the loss. The receive gain (G<sub>p</sub>) and transmit gain (G<sub>T</sub>) are set by the ratios of resistors R2, R1 and R6, R5, respectively (Figure 2).

The circuit can be analyzed as follows:

$$\begin{aligned} & V_{R} = - \frac{R2}{R1} \left( V_{TR} \right) + \left( 1 + \frac{R2}{R1} \right) \left( \frac{R4}{R3 + R4} \right) V_{y} \\ & V_{y} = - \frac{R6}{R5} V_{x} \end{aligned}$$

If R6/R5 is chosen to equal the loss in the transformer, it can be assumed that  $V_y$  is twice as high as  $V_{TX}$  (transmit portion of the total line signal). Since  $V_{TR} = V_{TX} + V_{RX}$  and  $V_y = 2V_{TX'}$

$$\begin{split} &V_{R} = - \ \frac{R2}{R1} \Big( V_{TX} + V_{RX} \Big) + \Big( 1 + \frac{R2}{R1} \Big) \Big( \frac{R4}{R3 + R4} \Big) 2 V_{TX} \\ &= - \ \frac{R2}{R1} \ V_{RX} + \left[ \Big( 1 + \frac{R2}{R1} \Big) \Big( \frac{2R4}{R3 + R4} \Big) - \frac{R2}{R1} \right] V_{TX} \end{split}$$

To eliminate any transmit signal from appearing at the received signal input, the second term in the above equation must be set to zero, giving:

$$\left(1 + \frac{R2}{R1}\right) \left(\frac{2R4}{R3 + R4}\right) = \frac{R2}{R1}$$

Solving for R3/R4:

$$\frac{R3}{R4} = 1 + \frac{2R1}{R2}$$

Additionally,

$$G_R = \frac{R^2}{R^2}$$

and  $G_T = \frac{R^6}{R^5}$

These equations can be solved to select component values that meet the desired requirements. For example, if the transmit and receive

loss in the coupling transformer is 2.5 dB, then:

$$\frac{R2}{R1} = INV \operatorname{Log}\left(\frac{G_{RdB}}{20}\right) = INV \operatorname{Log}\left(\frac{2.5}{20}\right) = 1.333$$

Similarly,

$$\frac{R6}{R5} = 1.333$$

and  $\frac{R3}{R4} = 2.5$

Some typical values are:

R1=20K $\Omega$ , R2=27K $\Omega$ , R3=13K $\Omega$ , R4= 5.1K $\Omega$ , R5=20K $\Omega$ , and R6=27K $\Omega$

It should be noted that the transmit amplifier is only needed to overcome the loss in line coupling. It can be eliminated since the transmit signal level specification is typically stated as a maximum. Amplifier B, resistors R5 and R6, and capacitor C1 can be eliminated, and point X can be connected to point Y in the circuit of Figure 2 to achieve a more cost effective external hybrid arrangement.

The SC11054 with the internal hybrid may also be used on a 4-wire system where the transmit and

receive signals are kept separate. In this mode, the "Hybrid" code must be turned off. The transmit signal is connected to a 600  $\Omega$  line transformer through a 600  $\Omega$  resistor.

#### **Tone Generator**

The tone generator section consists of a DTMF generator, V.22 guardtone, and 1300 and 2100 Hz tone generators. The DTMF generator produces all of the tones corresponding to digits 0 through 9 and A, B, C, D, \*, and # keys. The V.22 guard-tone generator produces either 550 Hz or 1800 Hz. Selection of either the 550 Hz or 1800 Hz tone will cascade the corresponding notch filter with the low-band filter. The tones are selected by applying appropriate codes through the tone control register. Before a tone can be generated, tone mode must be selected. Facility is also provided to generate single tones corresponding to 1300, 1100, 464 and 2100 Hz and the individual rows or columns

of the DTMF signal.

#### **Audio Output Stage**

A programmable attenuator that can drive a load impedance of 50K Ohms is provided to allow monitoring of the received line signal through an external speaker. The attenuator is connected to the output of the hybrid. Four levels of attenuation-no attenuation, 6 dB attenuation, 12 dB attenuation, and squelch are provided through the ALC1 and ALC0 audio output level control codes. Output of the attenuator is available on the audio output pin where an external audio amplifier (LM386 type) can be connected to drive a low impedance speaker. The output can directly drive a high impedance transducer, but the volume level will be low.

#### **Clock Input**

CLKIN (Pin 22) of the SC11054 should be connected to a 9.8304 MHz clock source with an accuracy of ±0.01%.

Figure 2. Using an External Hybrid with the SC11054

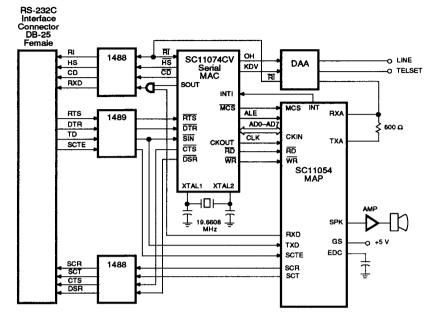

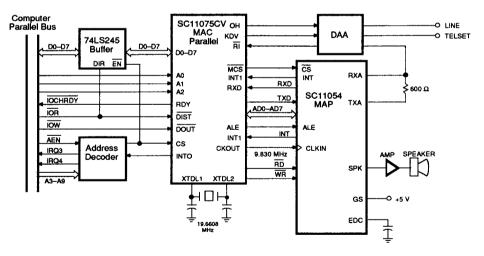

#### **FUNCTIONAL DESCRIPTION OF THE SC11011 CONTROLLER**

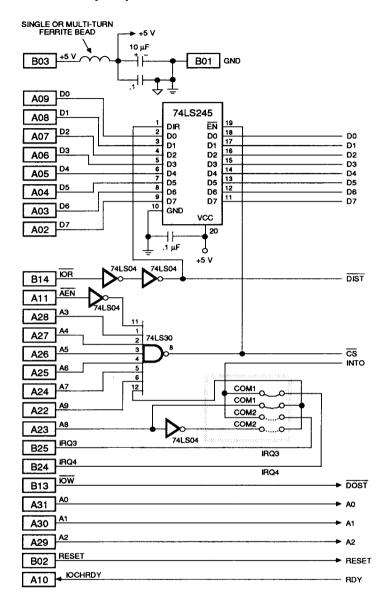

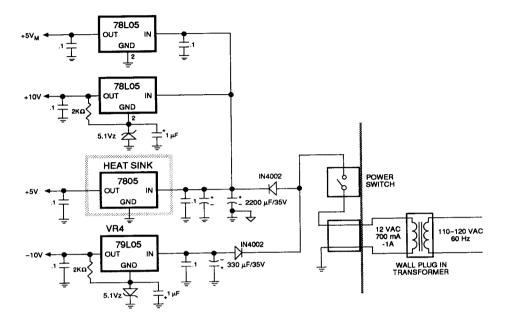

The SC11011 modem controller, implemented in Sierra's CMOS process, was designed specifically to handle all of the modem control functions, as well as the interface to a system bus or an RS-232 serial interface. Besides including a 16-bit microprocessor, 8k by 8 bytes of ROM and 128 by 8 bytes of RAM, it also contains the functionality of a 82C50B UART, greatly simplifying the interface to a parallel system bus, such as the one used in IBM's PC. In fact, a complete, Hayes compatible modem with Sendfax capability for the PC consists of the SC11011 controller with external memory, the SC11054 modem and the DAA. All of the popular communications software written for the PC will work with the SC11054/SC11011 set.

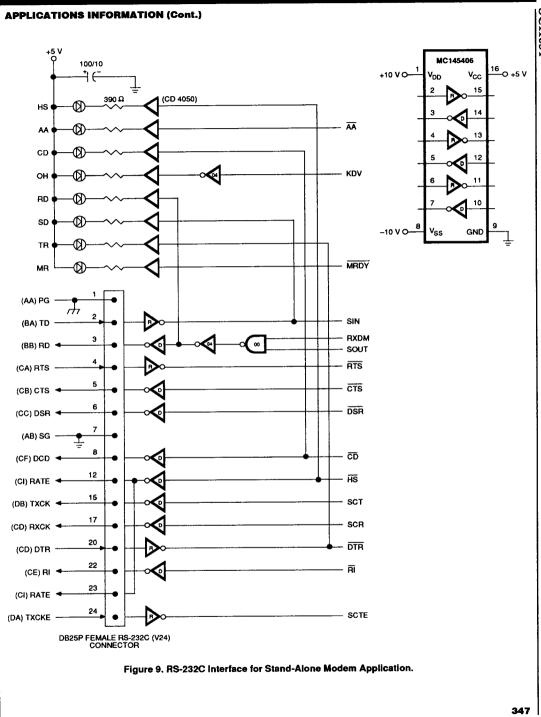

The SC11011 can be configured for RS-232 applications. The difference is that the UART is wired so that the serial data from the RS-232 port is converted to parallel data handled by the internal processor. Pins are provided for connecting the familiar switches and indicator lamps found on most stand-alone modems, although the switches and lamps are not needed for operation—all of the switch settings can be done through software.

The controller receives an 8-bit signal sample from the SC11054 and performs adaptive equalization, carrier phase recovery, data decode, and descrambling. The controller is configured for parallel or serial applications by the firmware. The controller is designed by using a 16-bit 2900 processor to perform the digital signal processing and the control functions. Its instruction set is a subset of the Intel 8096 instruction set, but operates faster than the 8096.

The SC11011 provides a standard 5V logic level interface—RS-232 drivers are required to interface to the port. Firmware for external

memory is available for the SC11054. It includes the Hayes "AT" command set, and T.30 protocol. When used with the SC11011 controller, it emulates a Hayes-type stand-alone or internal modem with Sendfax.

The SC11011 is available in a 68 pin PLCC. The 68 pin package allows the controller to access external ROM of up to 32K bytes and external RAM of up to 16K bytes. This allows users to customize their own software, and provides a means for software development. The serial controller can talk to both an SC11054 and an SC22201 (EERAM).

The SC11011 requires a single +5 V power supply. Besides the interface for the SC11054 modem, when the SC11011 controller is used for internal applications, it has an eight-bit data port, three address lines, a chip select input, an interrupt line, and the DOST and DIST control lines found in the 82C50B UART. It also has control lines for ring indication, the off-hook relay, and a data/voice relay; these lines connect to the DAA.

When used in RS-232 applications the SC11011's, eight-bit port becomes the switch input lines, and the address, chip select, INTO, DIST and DOST lines become the lines for the RS-232 interface, and modem status. These lines are also used to drive the LEDs. Internally, all of these lines are treated as programmable I/O ports under software control.

The interface to the SC11054 is via an 8-bit address/data bus and the control lines for read and write. The same interface is used for access to an electrical erasable random access memory (SC22201). There are six clock multiplexed address/data bus cycles. A ready signal is provided for the interface to a high speed PC-AT type bus cycle. The 68 pin package, has 15 extra address

lines and chip selects for external ROM and external RAM interfaces.

The SC11011 is truly an ASIC DSP & controller—it is designed to control a modem or other peripheral that operates at a moderately slow data rate up to 2400 bits per second. What's unique about the SC11011, for example, is that it allows a slow peripheral to interface to a high speed bus without making the main processor add unnecessary wait states.

This is done through the UART interface and the on-chip registers which look somewhat like dual port registers. The main processor can write to and read from them at will, while the on-chip controller can do the same. The controller was designed this way because most communications software has to have unrestrained access to the UART registers. To make the SC11011 compatible with this software, the registers were included.

The internal processor monitors the registers to determine the mode of operation—command mode or data mode; at power-up, it is automatically put in the command mode and it looks for instructions. Once carrier is detected, it goes into the data mode, and stays there until an escape sequence is entered, just like a Hayes-type modem. The escape sequence is three + signs—+++—in the default mode, but it can be changed in the software.

The actual processor contains a 16-bit data path and can execute 54 instructions with three different addressing modes: direct, indirect, and immediate. There is 8K by 8 of ROM on the chip for program storage.

To the system bus, the SC11011 looks and acts like an 8250B UART. Communications software written for this UART will work with the SC11011.

IMAGE UNAVAILABLE

#### PIN DESCRIPTIONS

| PIN NO.     | PIN NAME         | DESCRIPTION                                                                                                                                                                                                                                       |  |

|-------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

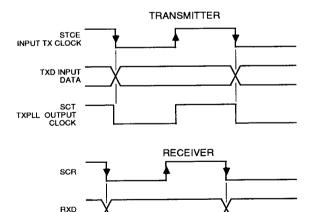

| 1           | SCR              | Synchronous Clock Receive (Data set source); Output; TTL; Used only in bit synchronous mode; Recovered by the Receiver Phase Locked Loop from the far end modem. Data on RXD is valid at the rising edge of this clock.                           |  |

| 2           | V <sub>REF</sub> | Reference Ground; Generated inside the chip and is equal to $V_{CC}/2$ .                                                                                                                                                                          |  |

| 3           | SCT              | Synchronous Clock Transmit (Data set source); Output; TTL; Used only in bit synchronous mode; Generated internally by the SC11024 Clock Generator; Rate = 1200 Hz ±0.01% or 2400 Hz ±0.01%.                                                       |  |

| 4           | SCTE             | Synchronous Clock Transmit External (DTE source); Input; TTL; Used only in bit synchronous mode; Data on TXD line is latched by the SC11024 at the rising edge of this clock. Clock rate = 1200 Hz ±0.01% or 2400 Hz ±0.01%.                      |  |

| 5           | AUDIO            | Audio output; The hybrid output is passed through a programmable attenuator and fed to this analog pin. Four different levels can be attained by controlling bit 0 and bit 1 of the AUDIO register as specified under AUDIO register description. |  |

| 6           | EDC              | Capacitor for energy detect; A $1.0\mu\text{F}$ capacitor should be connected between this pin and AGND.                                                                                                                                          |  |

| 7           | DGND             | Digital ground                                                                                                                                                                                                                                    |  |

| 8           | CS               | Chip Select; Input; TTL; Active low.                                                                                                                                                                                                              |  |

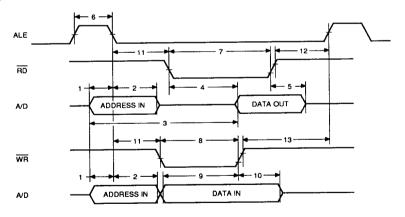

| 9           | WR               | Write; Input; TTL; Normally high; Data on AD7-AD0 is written into the SC1 registers at the rising edge of this pulse.                                                                                                                             |  |

| 10          | RD               | Read; Input; TTL; Normally high; Data on AD7–AD0 is to be read by the processor at the rising edge of this pulse.                                                                                                                                 |  |

| 12,13,17,18 | AD1-AD4          | Multiplexed address/data bus (8-bits); Input/Output; TTL; A/D4-A/D1 (4-bits) are used for multiplexed addressing of internal registers.                                                                                                           |  |

| 14          | AGND             | Analog Ground                                                                                                                                                                                                                                     |  |

| 15          | RXA              | Receive analog; Input                                                                                                                                                                                                                             |  |

| 16          | TXA              | Transmit analog; Output                                                                                                                                                                                                                           |  |

| 11,19–21    | D0, D5-D7        | Bits 0, 5, 6 and 7 are don't cares as far as address is concerned.                                                                                                                                                                                |  |

| 22          | CLKIN            | Clock input; 9.8304 MHz clock input from the controller.                                                                                                                                                                                          |  |

| 23          | GS               | Gain Select to compensate for loss in line coupling transformer. When left open or tied to AGND, the compensation is 0 dB; connected to VREF, +2 dB compensation is provided; And when tied to $V_{CC'}$ the compensation is +3 dB.               |  |

| 24          | ALE              | Address Latch Enable; Input; TTL; The address on A/D4–A/D1 is latched into the SC11054 Address decoder at the falling edge of this normally low pulse.                                                                                            |  |

| 25          | INT              | Interrupt; Output; TTL; Normally low; A short (13 µs typical) positive pulse is generated after all A to D conversions are completed.                                                                                                             |  |

| 26          | RXD              | Received Data; Output; TTL                                                                                                                                                                                                                        |  |

| 27          | TXD              | Transmit Data; Input; TTL                                                                                                                                                                                                                         |  |

| 28          | v <sub>cc</sub>  | +5 V supply                                                                                                                                                                                                                                       |  |

#### REGISTERS

There are fourteen 8-bit registers interfacing to the microprocessor bus. Six of these registers can only be read by the processor (called READ registers) and the remaining eight can be written into by the processor (called CONTROL registers). Bit 1 of the "Tone" register can be read and written by the processor, Table 1 shows the address and bit assignments for these registers.

A chip select pin is provided for multiperipheral addressing by the processor.

**Table 1. READ Registers**

| А  | DDRE       | SS BIT | rs | NAME    | MSB |        |         | BIT NU     | MBER   |        |      | LSB |

|----|------------|--------|----|---------|-----|--------|---------|------------|--------|--------|------|-----|

| A4 | <b>A</b> 3 | A2     | A1 |         | 7   | 6      | 5       | 4          | 3      | 2      | 1    | 0   |

| 0  | 0          | 0      | 0  | Q1      | Q17 | Q16    | Q15     | Q14        | Q13    | Q12    | Q11  | Q10 |

| 0  | 0          | 0      | 1  | I1      | I17 | I16    | I15     | I14        | I13    | I12    | II1  | 110 |

| 0  | 0          | 1      | 0  | Q2      | Q27 | Q26    | Q25     | Q24        | Q23    | Q22    | Q21  | Q20 |

| 0  | 0          | 1      | 1  | IŽ      | 127 | I26    | 125     | <b>124</b> | I23    | 122    | I21  | I20 |

| 0  | 1          | 0      | 0  | Status  | X   | X      | FLAGDET | AGCO       | TD2100 | TD2225 | FSKD | ED  |

| 0  | 1          | 0      | 1  | FAXV21R | R7  | R6     | R5      | R4         | R3     | R2     | R1   | R0  |

| 0  | 1          | Х      | 1  | Unused  |     | Unused |         |            |        |        |      |     |

| 0  | 1          | 1      | Х  | Unused  |     | Unused |         |            |        |        |      |     |

#### STATUS Register: Address (A4-A1) = 0100

| BIT NUMBER | BIT NAME | DESCRIPTION                                                                                                                  |

|------------|----------|------------------------------------------------------------------------------------------------------------------------------|

| Bits 7-6   | Unused   |                                                                                                                              |

| Bits 5     | FLAGDET  | Flag Sequence detector output. When set, flag sequence is present in V.21FAX mode.                                           |

| Bit 4      | AGCO     | Status of internal 1-bit AGC. When this bit is set, RXA signal is amplified by $8\ dB$ before entering the bandpass filters. |

| Bit 3      | TD2100   | 2100 Hz tone detector output. TD2100=1 when this tone is present.                                                            |

| Bit 2      | TD2225   | 2225 Hz tone detector output. TD2225=1 when this tone is present.                                                            |

| Bit 1      | FSKD     | Received FSK data. FSKD = 1 when mark is received.                                                                           |

| Bit 0      | ED       | Energy detect circuit output. ED = 1 when energy detected.                                                                   |

Note: When reading unused bits, the corresponding bus lines will not be driven by the SC11054 and will be floating.

#### FAXV21R Register: Address (A4-A1) = 0101

| BIT NUMBER | BIT NAME | DESCRIPTION                                                                                                                                                                          |

|------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bits 7–0   | R7-R0    | In V.21 FAX receive mode this register will be loaded by received data and should be read every eighth interrupt pulse. LSB (R0) corresponds to the data bit received first in time. |

#### Table 1a. READ Registers

| Q1 Register: Stores midbaud inphase samp I1 Register: Stores midbaud quadrature s Q2 Register: Stores endbaud inphase samp I2 Register: Stores endbaud quadrature s | ample output of ADC. ple output of ADC. |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

Note: All samples are represented in two's complement form.

Table 2. CONTROL Registers

| ΑĽ | DDR | ESS 1 | BITS       | NAME  |       | 7178    |         | BIT NU  | MBER   |      |                  |       |

|----|-----|-------|------------|-------|-------|---------|---------|---------|--------|------|------------------|-------|

| A4 | А3  | A2    | <b>A</b> 1 |       | 7     | 6       | 5       | 4       | 3      | 2    | 1                | 0     |

| 1  | 0   | 0     | 0          | TXCR  | BR2   | HYBRID  | TXSEL2  | TXSEL1  | TXSEL0 | SQT  | BR1              | BRO   |

| 1  | 0   | 0     | 1          | MCRA  | SLAVE | LCK/INT | RNGX    | SYNC    | WLS1   | WLS0 | $A/\overline{O}$ | RXMRK |

| 1  | 0   | 1     | 0          | MCRB  | BR3   | PD      | TONDETE | CPM     | ALB    | TL2  | TL1              | TL0   |

| 1  | 0   | 1     | 1          | TONE  | X     | HNDSHK  | TONEON  | DTMF    | D3     | D2   | D1               | D0    |

| 1  | 1   | 0     | 0          | PGCR  | X     | AGCVT   | G5      | G4      | G3     | G2   | G1               | G0    |

| 1  | 1   | 0     | 1          | DATA  | Х     | PLLJAM  | PLLFRZ  | PLLFAST | RD3    | RD2  | RD1              | RD0   |

| 1  | 1   | 1     | 0          | AUDIO | Х     | DISS    | PGCZ    | TST2    | TST1   | TST0 | ALC1             | ALC0  |

| 1  | 1   | 1     | 1          | FAXR  | B7    | В6      | B5      | B4      | B3     | B2   | B1               | В0    |

#### CONTROL REGISTERS

BIT NUMBER

Bit 7

Bit 3

BIT NAME

BR2

TXSEL0

#### Transmit Control Register (TXCR): Address (A4-A1) = 1000

(Note: When writing into these registers, the bus lines corresponding to the unused bits are ignored by the SC11054.)

This bit in conjunction with BR3, BR1 and BR0 selects bit rate.

| Bit 6 | HYBRID        |

|-------|---------------|

| Bit 5 | TXSEL2        |

| Bit 4 | TXSEL1<br>and |

DESCRIPTION

When set, the transmitter output (TXA) is connected to the inverting input of the receive buffer to allow the use of the on-chip hybrid circuit for 2 to 4 wire conversion.

Transmit Select bits. These 3 bits determine the data transmitted by the transmitter according to the following table:

| TXSEL2 | TXSEL1 | TXSELO | TRANSMITTED DATA                               |

|--------|--------|--------|------------------------------------------------|

| 0      | 0      | 0      | External data sent by DTE.                     |

| 0      | 0      | 1      | Unscrambled S1 (Note 1).                       |

| 0      | 1      | 0      | Unscrambled Space.                             |

| Õ      | 1      | 1 1    | Unscrambled Mark.                              |

| 1      | 0      | 0      | Scrambled RX. Digital loop back mode (Note 2). |

| î      | 0      | 1 1    | Scrambled Reversals (Notes 3 and 4).           |

| î      | 1      | 0      | Scrambled Space (Note 4).                      |

| î      | 1      | l i    | Scrambled Mark (Note 4).                       |

Note 1: S1 is a pattern of 0011 transmitted at 1200 bps rate regardless of BR1. If in FSK mode (BR0 = 1), then reversals are sent. This pattern cannot be sent at

Note 2: In this mode, the received data, after being descrambled, is sent back to the scrambler. The modem will automatically go to the Synchronous mode. Slave bit has to be set.

Note 3: Reversals are continuous streams of 01.

Note 4: When in FSK mode (BR0 = 1), TXSEL2 is ignored since scrambling is not applicable.

SQT Bit 2

When this bit is set, the transmitter is squelched by connecting the output of MUX1 (see the block diagram) to analog ground.

BR1 Bit 1 and BR<sub>0</sub> Bit 0

Bit Rate Selection bits based on the following table:

| BR3 | BR2 | BR1 | BRO | BIT RATE             |

|-----|-----|-----|-----|----------------------|

| 0   | 0   | 0   | 0   | 2400 bps V.22 bis    |

| 0   | 0   | 1   | 0   | 1200 bps V.22/212A   |

| 0   | 0   | 0   | 1   | 0-300 bps Bell 103   |

| 0   | 0   | 1   | 1   | 0-300 bps CCITT V.21 |

| 0   | 1   | 0   | 0   | 4800 bps V.27        |

| Ô   | 1   | 1   | 0   | 2400 bps V.27        |

| X   | 1   | 0   | 1   | N.A.                 |

| 1   | x   | 0   | 1   | N.A.                 |

| x   | 1   | 1   | 1   | 0-300 bps V.21 FAX   |

| 1   | х   | 1   | 1   | 0-300 bps V.21 FAX   |

| 1   | 0   | 0   | 0   | 9600 bps V.29        |

| 1   | ló  | 1   | 0   | 7200 bps V.29        |

| 1   | 1   | X   | 0   | N.A.                 |

| CONTROL | REGISTERS | (Cont.) |

|---------|-----------|---------|

|---------|-----------|---------|

| Mode Contro | l Register A     | (MCRA):                                                                                                                                                                                                                                                                                                                           | Address                 | s (A4-A1) = 1001                                                                       | - 1 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - |  |  |

|-------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| BIT NUMBER  | BIT NAME         | DESCRIPTION                                                                                                                                                                                                                                                                                                                       |                         |                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| Bit 7       | SLAVE            |                                                                                                                                                                                                                                                                                                                                   |                         | timing will be used as clock source for transmotor slave mode                          | nitter. LCK/INTB and SYNC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| Bit 6       | LCK/INTB         | Determines the clock source for the transmitter. When this bit is set, the clock source externally provided on SCTE (pin 4), and when cleared, it is internally generated (SCT).                                                                                                                                                  |                         |                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|             |                  | This bit o<br>When in                                                                                                                                                                                                                                                                                                             | can select<br>Digital L | the clock source independent of Sync/Asyndoop-Back mode, the clock source will be forc | mode selection (see below).<br>ed to the Slave mode (SCR).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| Bit 5       | RNGX             | Range extender for the receiver Sync/Async converter. When set, the receiver Sync/Async can insert up to one stop bit per four (8, 9, 10 or 11-bit) characters to compensate for a far end DTE being up to 2.3% over speed. The transmitter Async/Syncalways handles this overspeed condition regardless of this bit's condition. |                         |                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| Bit 4       | SYNC             | When set, operate in bit synchronous mode; when clear, operate in character asynchronous mode. When in Digital Loop-Back mode, the SC11046 will be forced to the Synchronous mode.                                                                                                                                                |                         |                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| Bit 3       | WLS1             | Word length select bits in asynchronous mode, according to the following table:                                                                                                                                                                                                                                                   |                         |                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| Bit 2       | and<br>WLS0      | WLS1                                                                                                                                                                                                                                                                                                                              | WLS0                    | NUMBER OF BITS PER CHARACTER                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|             |                  | 1<br>1<br>0<br>0                                                                                                                                                                                                                                                                                                                  | 0<br>1<br>0<br>1        | 8<br>9<br>10<br>11                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| Bit 1       | $A/\overline{O}$ | When set, operate in answer mode; when clear, operate in originate mode.                                                                                                                                                                                                                                                          |                         |                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| Bit 0       | RXMARK           | When set, the RXD pin is clamped to the high logical level.                                                                                                                                                                                                                                                                       |                         |                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| Mode Control Register E | 3 (MCRB): | Address (A4-A1) = 1010 |

|-------------------------|-----------|------------------------|

|-------------------------|-----------|------------------------|

| BIT NUMBER | BIT NAME   | DESCRIPTION                                                                                                                                                                                                                                      |     |     |                      |                         |  |

|------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|----------------------|-------------------------|--|

| Bit 7      | BR3        | This bit in conjunction with BR2-BR0 selects the bit rate.                                                                                                                                                                                       |     |     |                      |                         |  |

| Bit 6      | PD         | When this bit is set, chip will be powered down. When cleared normal operation is restored.                                                                                                                                                      |     |     |                      |                         |  |